## 13-bit Sin/D CONVERTER WITH SIGNAL CALIBRATION (CHaus

Rev E2, Page 1/32

#### **FEATURES**

- ♦ Resolution of up to 8,192 angle steps per sine period

- ♦ Binary and decimal resolution settings, e.g. 500, 512, 1000, 1024; programmable angle hysteresis

- Count-safe vector follower principle, real-time system with 70 MHz sampling rate

- ♦ Conversion time of just 250 ns including amplifier settling

- ♦ Direct sensor connection; selectable input gain

- ♦ Input frequency of up to 250 kHz

- ♦ Signal conditioning for offset, amplitude and phase

- ♦ A/B quadrature signals of up to 3.75 MHz with adjustable minimum transition distance

- ♦ Zero signal processing, adjustable in index position and width

- ♦ Absolute angle output via fast serial interface (BiSS, SSI)

- ♦ Permanent bidirectional memory access to parameters and OEM data by BiSS C

- ♦ Period counting with up to 24 bits

- ♦ Error monitoring of frequency, amplitude and configuration

- ♦ Device setup from serial EEPROM or using BiSS

- ♦ ESD protection and TTL-/CMOS-compatible outputs

#### **APPLICATIONS**

- ♦ Interpolator IC for angle resolution from sine/cosine sensor signals

- Optical encoders

- MR sensor systems

#### **PACKAGES**

TSSOP20 RoHS compliant

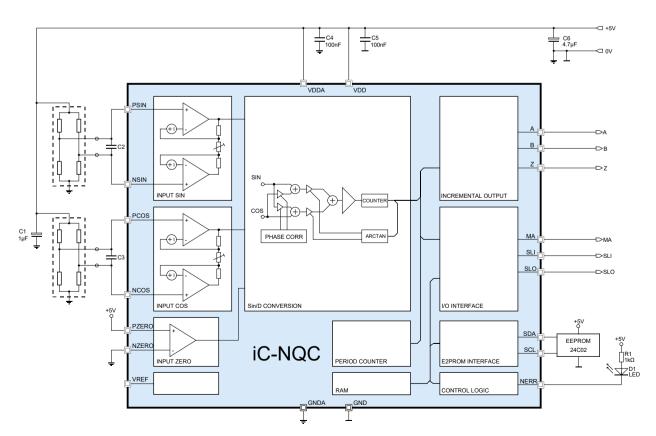

#### **BLOCK DIAGRAM** PSIN +) ∄ +)-| INCREMENTAL OUTPUT NSIN INPUT SIN PCOS $\oplus$ SLO + SLI Ì I/O INTERFACE -(+)-SDA NCOS INPUT COS Sin/D CONVERSION PZERO SCL NZERO E2PROM iC-NQC PERIOD COUNTER INPUT ZERO NERR VREF CONTROL LOGIC RAM

GNDA

GND

## 13-bit Sin/D CONVERTER WITH SIGNAL CALIBRATION

Rev E2, Page 2/32

#### **DESCRIPTION**

iC-NQC is a monolithic A/D converter which, by applying a count-safe vector follower principle, converts sine/cosine sensor signals with a selectable resolution and hysteresis into angle position data.

This absolute value is output via a bidirectional, synchronous-serial I/O interface in BiSS C protocol and trails a master clock rate of up to 10 Mbit/s. Alternatively, this value can be output so that it is compatible with SSI in Gray or binary code, with or without error bits. The device also supports double transmission in SSI ring mode.

Signal periods are logged quickly by a 24-bit period counter that can supplement the output data with an upstream multiturn position value.

At the same time any changes in angle are converted into incremental A QUAD B signals. Here, the minimum transition distance can be stipulated and adapted to suit the system on hand (cable length, external counter). A synchronized zero index Z is generated if enabled by PZERO and NZERO.

The front-end amplifiers are configured as instrumentation amplifiers, permitting sensor bridges to be directly connected without the need for external resistors. Various programmable D/A converters are available for the conditioning of sine/cosine sensor signals with regard to offset, amplitude ratio and phase errors (offset compensation by 8-bit DAC, gain ratio by 5-bit DAC, phase compensation by 6-bit DAC).

The front-end gain can be set in stages graded to suit all common complementary sensor signals of approximately 20 mVpp to 1.5 Vpp and also non-complementary sensor signals of 40 mVpp to 3 Vpp, respectively.

The device can be configured using two bidirectional interfaces, the EEPROM interface from a serial EEP-ROM with I<sup>2</sup>C interface, or the I/O interface in BiSS C protocol. Free storage space on the EEPROM can be accessed via BiSS for the storage of additional data.

After a low voltage reset, iC-NQC reads in the configuration data including the check sum (CRC) from the EEPROM and repeats the process if a CRC error is detected.

## 13-bit Sin/D CONVERTER WITH SIGNAL CALIBRATION (CHaus

Rev E2, Page 3/32

#### CONTENTS

| PACKAGING INFORMATION                                 | 4             | I/O INTERFACE: BISS C PROTOCOL              | 20 |

|-------------------------------------------------------|---------------|---------------------------------------------|----|

| PIN CONFIGURATION                                     |               | Interface Parameters With BiSS C Protocol . | 20 |

| TSSOP20 4.4 mm, lead pitch 0.65 mm .                  | 4             | Example of BiSS Data Output                 | 21 |

| PACKAGE DIMENSIONS                                    | 5             | Register Communication                      | 21 |

| ABSOLUTE MAXIMUM RATINGS                              | 6             | Internal Reset Function                     | 21 |

| ADOCEOTE MAXIMOM NATINGO                              | J             | Short BiSS Timeout                          | 21 |

| THERMAL DATA                                          | 6             |                                             |    |

| =                                                     | _             | I/O INTERFACE: SSI Protocol                 | 23 |

| ELECTRICAL CHARACTERISTICS  CHARACTERISTICS: Diagrams | <b>7</b><br>9 | Examples of SSI Data Output                 | 24 |

| OPERATING REQUIREMENTS                                | 10            | EEPROM INTERFACE                            | 25 |

| I/O Interface                                         | 10            | Example of CRC Calculation Routine          | 25 |

| PARAMETER and REGISTER                                | 11            | STARTUP BEHAVIOR                            | 26 |

|                                                       |               | Startup With A Configured EEPROM            | 26 |

| SIGNAL CONDITIONING                                   | 12            | Startup Without An EEPROM                   | 26 |

| CONVERTER FUNCTIONS                                   | 13            | Initialization After Configuration Failure  | 26 |

| MAXIMUM POSSIBLE CONVERTER                            |               | APPLICATION NOTES                           | 28 |

| FREQUENCY                                             | 14            | Principle Input Circuits                    | 28 |

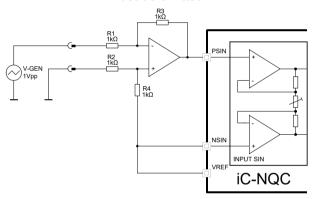

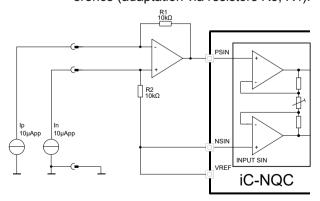

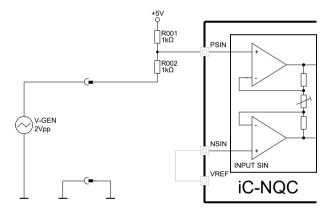

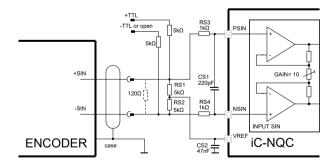

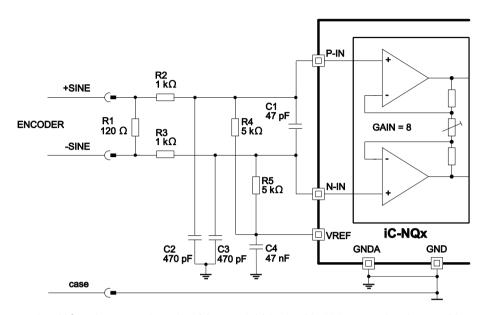

| Serial Data Output                                    | 14            | Input Circuit for Sine Encoders (1 Vpp)     | 28 |

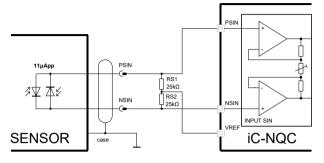

| Incremental Output to A, B and Z                      | 15            | Basic Circuit for MR Sensors                | 29 |

| INCREMENTAL SIGNALS                                   | 16            | EVALUATION BOARD                            | 29 |

| SIGNAL MONITORING and ERROR MESSAGES                  | 18            | DESIGN REVIEW: Function Notes               | 30 |

| TEST FUNCTIONS                                        | 19            | REVISION HISTORY                            | 31 |

# 13-bit Sin/D CONVERTER WITH SIGNAL CALIBRATION (CHaus

Rev E2, Page 4/32

#### PACKAGING INFORMATION TSSOP20 (according to JEDEC Standard)

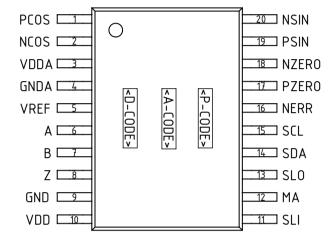

#### **PIN CONFIGURATION** TSSOP20 4.4 mm, lead pitch 0.65 mm

#### **PIN FUNCTIONS** Nama

| No. | Name             | Function                              |

|-----|------------------|---------------------------------------|

| 1   | PCOS             | Input Cosine +                        |

| 2   | NCOS             | Input Cosine -                        |

| 3   | VDDA 1           | +5 V Supply Voltage (analog)          |

| 4   | GNDA 1           | Ground (analog)                       |

| 5   | VREF             | Reference Voltage Output              |

| 6   | Α                | Incremental Output A                  |

|     |                  | Analog signal COS+ (TMA mode)         |

|     |                  | PWM signal for Offset Sine (calib.)   |

| 7   | В                | Incremental Output B                  |

|     |                  | Analog signal COS- (TMA mode)         |

|     |                  | PWM signal for Offset Cosine (calib.) |

| 8   | Z                | Incremental Output Z                  |

|     |                  | PWM signal for Phase/Ratio (calib.)   |

| _   | GND              | Ground                                |

|     | VDD              | +5 V Supply Voltage (digital)         |

|     | SLI <sup>2</sup> | I/O Interface, data input             |

|     | MA               | I/O Interface, clock line             |

|     | SLO              | I/O Interface, data output            |

| 14  | SDA              | EEPROM interface, data line           |

|     | 0                | Analog signal SIN+ (TMA mode)         |

| 15  | SCL <sup>3</sup> | EEPROM interface, clock line          |

|     |                  | Analog signal SIN- (TMA mode)         |

|     | NERR             | Error Input/Output, active low        |

|     | PZERO            | Input Zero Signal +                   |

|     | NZERO            | Input Zero Signal -                   |

|     | PSIN             | Input Sine +                          |

| 20  | NSIN             | Input Sine -                          |

IC top marking: <P-CODE> = product code, <A-CODE> = assembly code (subject to changes), <D-CODE> = date code (subject to changes);

<sup>&</sup>lt;sup>1</sup> External connections linking VDDA to VDD and GND to GNDA are required.

<sup>&</sup>lt;sup>2</sup> If only a single iC-NQC is used and no chain circuitry of multiple BiSS slaves, pin SLI can remain unwired or can be linked to ground (GND).

<sup>&</sup>lt;sup>3</sup> It is not permissible to pull down pin SCL during power-up.

## 13-bit Sin/D CONVERTER WITH SIGNAL CALIBRATION (CHaus

Rev E2, Page 5/32

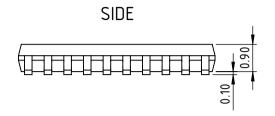

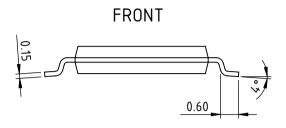

#### **PACKAGE DIMENSIONS**

## TOP 6.50 04.4 0.65 0.25

#### RECOMMENDED PCB-FOOTPRINT

All dimensions given in mm. Tolerances of form and position according to JEDEC MO-153

drb\_tssop20-1\_pack\_1, 8:1

# 13-bit Sin/D CONVERTER WITH SIGNAL CALIBRATION (CHaus

Rev E2, Page 6/32

#### **ABSOLUTE MAXIMUM RATINGS**

These ratings do not imply permissible operating conditions; functional operation is not guaranteed. Exceeding these ratings may damage the device.

| Item | Symbol    | Parameter                                                                                             | Conditions                                                                                                                                                                           |      |      | Unit |

|------|-----------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

| No.  |           |                                                                                                       |                                                                                                                                                                                      | Min. | Max. |      |

| G001 | VDDA      | Voltage at VDDA                                                                                       |                                                                                                                                                                                      | -0.3 | 6    | V    |

| G002 | VDD       | Voltage at VDD                                                                                        |                                                                                                                                                                                      | -0.3 | 6    | V    |

| G003 | Vpin()    | Voltage at<br>PSIN, NSIN, PCOS, NCOS, PZERO,<br>NZERO, VREF, NERR, SCL,<br>SDA, MA, SLI, SLO, A, B, Z | V() < VDDA + 0.3 V<br>V() < VDD + 0.3 V                                                                                                                                              | -0.3 | 6    | V    |

| G004 | Imx(VDDA) | Current in VDDA                                                                                       |                                                                                                                                                                                      | -50  | 50   | mA   |

| G005 | Imx(GNDA) | Current in GNDA                                                                                       |                                                                                                                                                                                      | -50  | 50   | mA   |

| G006 | Imx(VDD)  | Current in VDD                                                                                        |                                                                                                                                                                                      | -50  | 50   | mA   |

| G007 | Imx(GND)  | Current in GND                                                                                        |                                                                                                                                                                                      | -50  | 50   | mA   |

| G008 | lmx()     | Current in<br>PSIN, NSIN, PCOS, NCOS, PZERO,<br>NZERO, VREF, NERR, SCL, SDA,<br>MA, SLI, SLO, A, B, Z |                                                                                                                                                                                      | -10  | 10   | mA   |

| G009 | llu()     | Pulse Current in all pins<br>(Latch-up Strength)                                                      | according to Jedec Standard No. 78;<br>Ta = 25 °C, pulse duration to 10 ms,<br>VDDA = VDDA <sub>max</sub> , VDD = VDD <sub>max</sub> ,<br>Vlu() = (-0.5+1.5) x Vpin() <sub>max</sub> | -100 | 100  | mA   |

| G010 | Vd()      | ESD Susceptibility at all pins                                                                        | HBM 100 pF discharged through 1.5 kΩ                                                                                                                                                 |      | 2    | kV   |

| G011 | Tj        | Junction Temperature                                                                                  |                                                                                                                                                                                      | -40  | 150  | °C   |

| G012 | Ts        | Storage Temperature Range                                                                             |                                                                                                                                                                                      | -40  | 150  | °C   |

#### THERMAL DATA

Operating Conditions: VDDA = VDD =  $5 V \pm 10 \%$

| Item | Symbol | Parameter                                                          | Conditions |      |      |      | Unit |

|------|--------|--------------------------------------------------------------------|------------|------|------|------|------|

| No.  |        |                                                                    |            | Min. | Тур. | Max. |      |

| T01  | Та     | Operating Ambient Temperature Range                                |            | -25  |      | 85   | °C   |

|      |        | (extended temperature range of -40 to 125 °C available on request) |            |      |      |      |      |

# 13-bit Sin/D CONVERTER WITH SIGNAL CALIBRATION (CHaus

Rev E2, Page 7/32

#### **ELECTRICAL CHARACTERISTICS**

Operating Conditions: VDDA = VDD = 5 V ±10 %, Tj = -40 ... 125 °C, unless otherwise stated.

| Item<br>No. | Symbol        | Parameter                                                                                                      | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Min.       | Тур.      | Max.          | Unit         |

|-------------|---------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|---------------|--------------|

| Total I     | Device        |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |           | '             |              |

|             |               | parameters beyond the operating co<br>within the individual application using                                  | onditions (with reference to independent voltage and properties of the properties of | supplies,  | for insta | nce)          |              |

| 001         | VDDA,<br>VDD  | Permissible Supply Voltage                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.5        |           | 5.5           | V            |

| 002         | I(VDDA)       | Supply Current in VDDA                                                                                         | fin() = 200 kHz; A, B, Z open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |           | 15            | mA           |

| 003         | I(VDD)        | Supply Current in VDD                                                                                          | fin() = 200 kHz; A, B, Z open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |           | 20            | mA           |

| 004         | Von           | Turn-on Threshold VDDA, VDD                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.2        |           | 4.4           | V            |

| 005         | Vhys          | Turn-on Threshold Hysteresis                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 200        |           |               | mV           |

| 006         | Vc()hi        | Clamp Voltage hi at<br>PSIN, NSIN, PCOS, NCOS,<br>PZERO, NZERO, VREF                                           | Vc()hi = V() - VDDA;<br>I() = 1 mA, other pins open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.3        |           | 1.6           | V            |

| 007         | Vc()lo        | Clamp Voltage Io at<br>PSIN, NSIN, PCOS, NCOS,<br>PZERO, NZERO, VREF, NERR,<br>SCL, SDA, MA, SLI, SLO, A, B, Z | I() = -1 mA, other pins open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -1.6       |           | -0.3          | V            |

| 800         | Vc()hi        | Clamp Voltage hi at<br>NERR, SCL, SDA, MA,<br>SLI, SLO, A, B, Z                                                | Vc()hi = V() - VDD;<br>I() = 1 mA, other pins open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.3        |           | 1.6           | V            |

| Input       | Amplifiers a  | and Signal Inputs PSIN, NSIN, PC                                                                               | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |           |               |              |

| 101         | Vos()         | Input Offset Voltage                                                                                           | Vin() and G() in accordance with Table GAIN; $G \ge 20$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -10        |           | 10            | mV           |

| 102         | TCos          | Input Offset Voltage Temperature Drift                                                                         | G < 20<br>see 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -15        | ±10       | 15            | mV<br>μV/K   |

| 103         | lin()         | Input Current                                                                                                  | V() = 0 V VDDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -50        |           | 50            | nA           |

| 104         | GA            | Gain Accuracy                                                                                                  | G() in accordance with Table GAIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 95         |           | 104           | %            |

| 105         | GArel         | Gain SIN/COS Ratio Accuracy                                                                                    | G() in accordance with Table GAIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 97         |           | 103           | %            |

| 106         | fhc           | Cut-off Frequency                                                                                              | G = 80<br>G = 2.667                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 150<br>630 |           |               | kHz<br>kHz   |

| 107         | SR            | Slew Rate                                                                                                      | G = 80<br>G = 2.667                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.3<br>6.0 |           |               | V/µs<br>V/µs |

| 108         | Vout()tma     | Permissible Internal Signal Level (Full-Scale Signal)                                                          | TMA mode: analog signal at A, B, SCL, SDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.5        |           | VDDA -<br>0.5 | V            |

| Sine-1      | Γο-Digital Co | onversion                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |           |               |              |

| 201         | AAabs         | Absolute Angle Accuracy without calibration                                                                    | referred to 360° input signal, G = 2.667,<br>Vin = 1.5 Vpp, HYS = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -1.0       |           | 1.0           | DEG          |

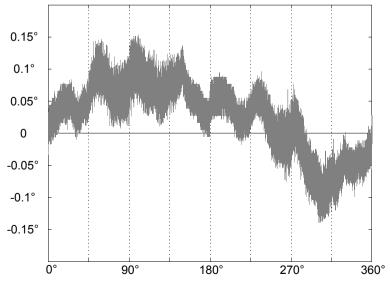

| 202         | AAabs         | Absolute Angle Accuracy after calibration                                                                      | referred to 360° input signal, HYS = 0, internal signal amplitude of 2 4 Vpp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -0.5       | ±0.35     | +0.5          | DEG          |

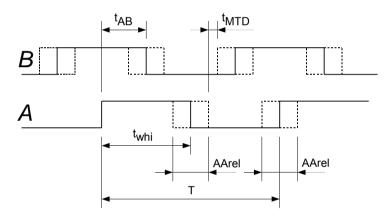

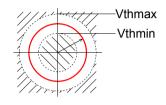

| 203         | AArel         | Relative Angle Accuracy                                                                                        | referred to signal periods at A, resp. B (see Fig. 1); G = 2.667, Vin = 1.5 Vpp, SELRES = 1024, FCTR = 0x0004 0x00FF, fin < fin <sub>max</sub> (see Table 11)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -10        |           | 10            | %            |

| Refere      | ence Voltag   | e Output VREF                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |           |               |              |

| 801         | VREF          | Reference Voltage                                                                                              | I(VREF) = -1 mA +1 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 48         |           | 52            | %<br>VDDA    |

| Oscill      | ator          | •                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |           |               |              |

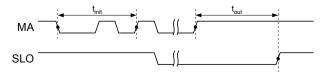

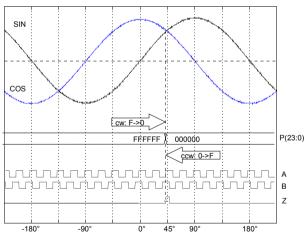

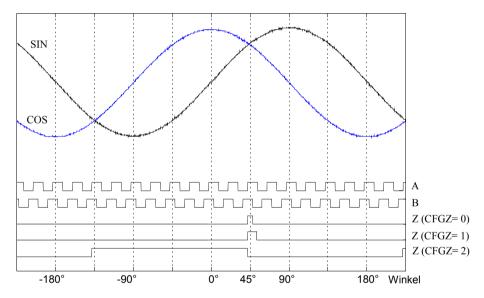

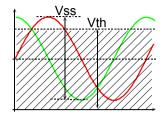

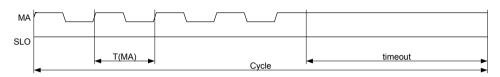

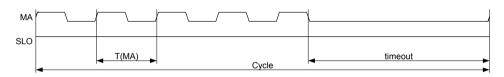

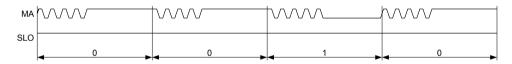

| A02         | fosc()        | Oscillator Frequency                                                                                           | presented at pin SCL with subdivision of 2048;<br>VDDA = VDD = 5 V ±10 %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 56         |           | 99            | MHz          |