### SIN/COS SIGNAL CONDITIONER WITH 1Vpp DRIVER

Rev D2, Page 1/29

#### **FEATURES**

PGA inputs to 500 kHz for differential and single-ended sensor signals

Selectable adaptation to voltage or current signals Flexible pin assignment due to signal path multiplexers

Sine/Cosine signal conditioning for offset, amplitude and phase

Separate index signal conditioning

Short-circuit-proof and reverse polarity tolerant output drivers (1 Vpp to 100  $\Omega$ )

Stabilized output signal levels due to sensor control

Signal and system monitoring with configurable alarm output

Supply voltage monitoring with integrated switches for reversed-polarity-safe systems

Excessive temperature protection with sensor calibration

I<sup>2</sup>C multimaster interface

Supply from 4.3 to 5 V, operation within -25(-40) to +100 °C Suitable for *SAFETY* applications

Verifyable chip release code

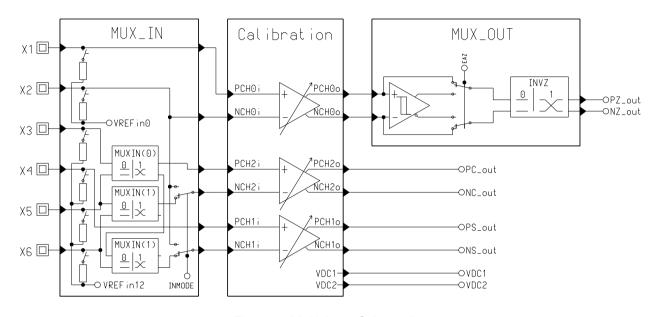

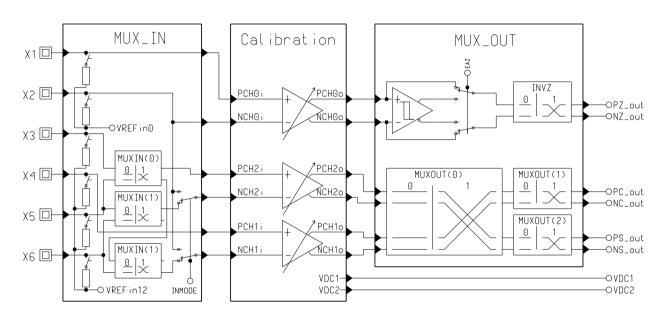

Version **iC-MSB2** with output multiplexer (not for *SAFETY*)

#### **APPLICATIONS**

Programmable sensor interface for optical and magnetic position sensors

Linear gauges and incremental encoders

Linear scales

#### **PACKAGES**

TSSOP20, TSSOP20-TP

Rev D2, Page 2/29

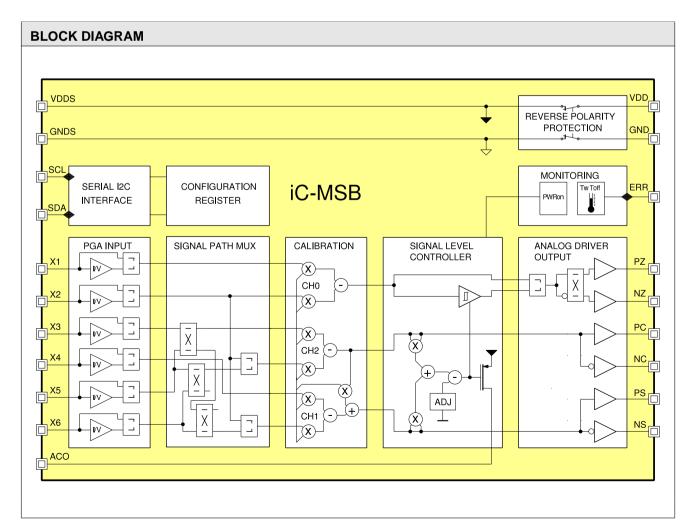

#### **DESCRIPTION**

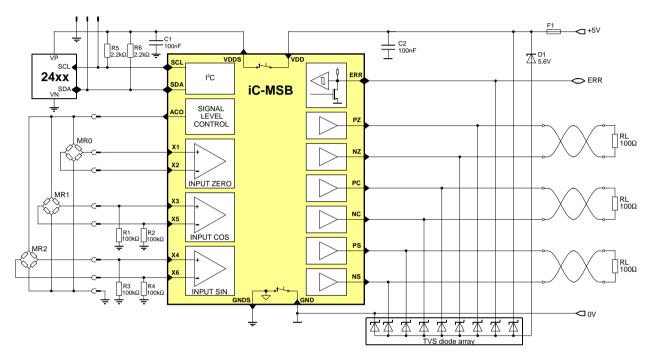

iC-MSB is a signal conditioner with line drivers for sine/cosine sensors which are used to determine positions in linear and angular encoders, for example.

Programmable instrumentation amplifiers with selectable gain levels permit differential or referenced input signals; at the same time the modes of operation differentiate between high and low input impedance. This adaptation of the iC to voltage or current signals enables MR sensor bridges or photosensors to be directly connected up to the device.

The integrated signal conditioning unit allows signal amplitudes and offset voltages to be calibrated accurately and also any phase error between the sine and cosine signals to be corrected. Separate zero signal conditioning settings can be made for the gain and offset; data is then output either as an analog or a differential square-wave signal (low/high level analogous to the sine/cosine amplitude).

For the stabilization of the sine and cosine output signal levels a control signal is generated from the conditioned and calibrated input signals which can power the transmitting LED of optical systems via the integrated 50 mA driver stage (output ACO). If MR sensors are connected this driver stage also powers the measuring bridges.

By tracking the sensor energy supply any signal variations and temperature and aging effects can be

compensated for and the set signal amplitude maintained with absolute accuracy. At the same time the control circuitry monitors both whether the sensor is functioning correctly and whether it is properly connected; signal loss due to wire breakage, short circuiting, dirt or aging, for example, is recognized when control thresholds are reached and indicated at alarm output ERR.

iC-MSB is protected against a reversed power supply voltage; the integrated voltage switch for loads of up to 20 mA extends this protection to cover the overall system. The analog output drivers are directly cable-compatible and tolerant to false wiring; if supply voltage is connected up to these pins, the device is not destroyed.

The device configuration and calibration parameters are CRC protected and stored in an external EEP-ROM; they are loaded automatically via the I2C interface once the supply voltage has been connected up.

A safety-technical analysis of iC-MSB on device level with the inclusion of layout and internal/external circuitry has been carried out together with the BGIA, St. Augustin. The result proved iC-MSB's capability for safety oriented applications with Siemens Sinumerik Controls.

Rev D2, Page 3/29

### **CONTENTS**

| PACKAGES                                          | 4  | SIGNAL PATH MULTIPLEXING: iC-MSB <sup>SAFETY</sup>                       | 18        |

|---------------------------------------------------|----|--------------------------------------------------------------------------|-----------|

| ABSOLUTE MAXIMUM RATINGS                          | 5  | EXTENDED SIGNAL PATH MULTIPLEXING: iC-MSB2 (not for safety applications) | 19        |

| THERMAL DATA                                      | 5  | SIGNAL CONDITIONING CH1, CH2                                             | 21        |

| ELECTRICAL CHARACTERISTICS                        | 6  | Gain Settings CH1, CH2                                                   |           |

| PROGRAMMING                                       | 10 | Phase Correction CH1 vs. CH2                                             |           |

| SERIAL CONFIGURATION INTERFACE                    |    | SIGNAL CONDITIONING CH0                                                  | 23        |

| (EEPROM)                                          | 13 | Gain Settings CH0                                                        | 23        |

| Example of CRC Calculation Routine                | 13 | Offset Calibration CH0                                                   |           |

| EEPROM Selection                                  | 13 |                                                                          |           |

| I <sup>2</sup> C Slave Mode (ENSL = 1)            | 14 | SIGNAL LEVEL CONTROL and SIGNAL MONITORING                               | 24        |

| BIAS SOURCE AND TEMPERATURE<br>SENSOR CALIBRATION | 15 | ERROR MONITORING AND ALARM OUTPUT  Error Protocol                        | <b>25</b> |

| OPERATING MODES                                   | 16 | I/O pin ERR                                                              | 25        |

| Calibration Op. Modes                             | 16 | TEMPERATURE MONITORING                                                   | 26        |

| Special Device Test Functions                     | 16 | TEMPERATURE MONITORING                                                   | 20        |

| Signal Filter                                     | 16 | REVERSE POLARITY PROTECTION                                              | 26        |

| TEST MODE                                         | 17 | APPLICATION HINTS                                                        | 27        |

| INPUT CONFIGURATIONS                              | 18 | Connecting MR sensor bridges for safety-related applications             | 27        |

|                                                   | 18 |                                                                          |           |

| Input Configurations                              | 10 | PLC Operation                                                            | 21        |

Rev D2, Page 4/29

### **PACKAGES**

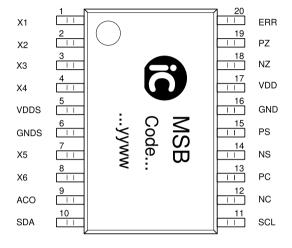

### PIN CONFIGURATION TSSOP20, TSSOP20-TP

### **PIN FUNCTIONS**

| No. | Name | Function                               |

|-----|------|----------------------------------------|

|     | X1   | Signal Input 1 (Index +)               |

| _   | X2   | Signal Input 2 (Index -)               |

|     | X3   | Signal Input 3                         |

|     | X4   | Signal Inout 4                         |

|     | VDDS |                                        |

| 3   | VDDO | (reverse polarity proof, load to 20 mA |

|     |      | max.)                                  |

| 6   | GNDS | Switched Ground                        |

|     |      | (reverse polarity proof)               |

| 7   | X5   | Signal Input 5                         |

| 8   | X6   | Signal Input 6                         |

| 9   | ACO  | Signal Level Controller,               |

|     |      | high-side current source output        |

| 10  | SDA  | Serial Configuration Interface,        |

|     |      | data line                              |

| 11  | SCL  | Serial Configuration Interface,        |

|     |      | clock line                             |

|     | NC   | Neg. Cosine Output                     |

|     | PC   | Pos. Cosine Output                     |

|     | NS   | Neg. Sine Output                       |

|     | PS   | Pos. Sine Output                       |

|     | GND  |                                        |

|     | VDD  | +4.5 to +5.5 V Supply Voltage          |

| _   | NZ   | Neg. Index Output                      |

|     | PZ   | Pos. Index Output                      |

| 20  | ERR  | Error Signal (In/Out),                 |

|     |      | Test Mode Trigger Input                |

To improve heat dissipation the *thermal pad* of the TSSOP20-TP package (bottom side) should be joined to an extended copper area which must have GNDS potential.

Rev D2, Page 5/29

### **ABSOLUTE MAXIMUM RATINGS**

These ratings do not imply operating conditions; functional operation is not guaranteed. Beyond these ratings device damage may occur.

| Item | Symbol | Parameter                                                                   | Conditions                           |      |            | Unit     |

|------|--------|-----------------------------------------------------------------------------|--------------------------------------|------|------------|----------|

| No.  |        |                                                                             |                                      | Min. | Max.       |          |

| G001 | V()    | Voltage at VDD, GND, PC, NC, PS, NS, PZ, NZ, ACO                            |                                      | -6   | 6          | V        |

| G002 | V()    | Voltage at ERR                                                              |                                      | -6   | 8          | V        |

| G003 | V()    | Pin-To-Pin Voltage between VDD,<br>GND, PC, NC, PS, NS, PZ, NZ, ACO,<br>ERR |                                      |      | 6          | V        |

| G004 | V()    | Voltage at X1X6, SCL, SDA                                                   |                                      | -0.3 | VDDS + 0.3 | V        |

| G005 | I(VDD) | Current in VDD                                                              |                                      | -100 | 100        | mA       |

| G006 | I()    | Current in VDDS, GNDS                                                       |                                      | -50  | 50         | mA       |

| G007 | I()    | Current in X1X6, SCL, SDA, ERR, PC, NC, PS, NS, PZ, NZ                      |                                      | -20  | 20         | mA       |

| G008 | I(ACO) | Current in ACO                                                              |                                      | -100 | 20         | mA       |

| G009 | Vd()   | ESD Susceptibility at all pins                                              | HBM 100 pF discharged through 1.5 kΩ |      | 2          | kV       |

| G010 | Ptot   | Permissible Power Dissipation                                               | TSSOP20<br>TSSOP20-TP                |      | 300<br>400 | mW<br>mW |

| G011 | Tj     | Junction Temperature                                                        |                                      | -40  | 150        | °C       |

| G012 | Ts     | Storage Temperature Range                                                   |                                      | -40  | 150        | °C       |

### THERMAL DATA

| Item | Symbol Parameter Conditions |  |                                                         | Unit       |      |            |     |

|------|-----------------------------|--|---------------------------------------------------------|------------|------|------------|-----|

| No.  |                             |  |                                                         | Min.       | Тур. | Max.       |     |

| T01  | Та                          |  | iC-MSB TSSOP20, iC-MSB2 TSSOP20<br>iC-MSB TSSOP20-TP    | -25<br>-40 |      | 100<br>115 | °C  |

| T02  | Rthja                       |  | TSSOP20 surface mounted to PCB according to JEDEC 51    |            | 80   |            | K/W |

| T03  | Rthja                       |  | TSSOP20-TP surface mounted to PCB according to JEDEC 51 |            | 35   |            | K/W |

Rev D2, Page 6/29

### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VDD = 4.3...5.5 V, Tj = -40...125 °C, IBN calibrated to 200 µA, reference point GNDS, unless otherwise stated.

| ltem<br>No. | Symbol       | Parameter                                            | Conditions                                                                                                                                                             | Min.                           | Тур.                           | Max.                           | Unit                         |

|-------------|--------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|------------------------------|

| Total       | Device       |                                                      |                                                                                                                                                                        |                                |                                |                                |                              |

| 001         | VDD          | Permissible Supply Voltage                           | Load current I(VDDS) < -10 mA                                                                                                                                          | 4.3<br>4.5                     |                                | 5.5<br>5.5                     | V                            |

| 002         | I(VDD)       | Supply Current in VDD                                | Tj = 27 °C, no load                                                                                                                                                    |                                | 25                             | 50                             | mA                           |

| 003         | I(VDDS)      | Permissible Load Current VDDS                        |                                                                                                                                                                        | -20                            |                                | 0                              | mA                           |

| 004         | Vcz()hi      | Clamp Voltage hi at all pins                         |                                                                                                                                                                        |                                |                                | 11                             | V                            |

| 005         | Vc()hi       | Clamp Voltage hi at inputs SCL, SDA                  | Vc()hi = V() - V(VDDS), I() = 1 mA                                                                                                                                     | 0.4                            |                                | 1.5                            | V                            |

| 006         | Vc()hi       | Clamp Voltage hi at inputs X1X6                      | Vc()hi = V() - V(VDDS), I() = 4 mA                                                                                                                                     | 0.3                            |                                | 1.2                            | V                            |

| 007         | Vc()lo       | Clamp Voltage lo at all pins                         | I() = -4 mA                                                                                                                                                            | -1.2                           |                                | -0.3                           | V                            |

| Signa       | I Conditioni | ng, Inputs X3X6                                      |                                                                                                                                                                        |                                |                                |                                |                              |

| 101         | Vin()sig     | Permissible Input Voltage Range                      | RIN12(3:0) = 0x01                                                                                                                                                      | 0.75                           |                                | VDDS<br>- 1.5                  | V                            |

|             |              |                                                      | RIN12(3:0) = 0x09                                                                                                                                                      | 0                              |                                | VDDS                           | V                            |

| 102         | lin()sig     | Permissible Input Current Range                      | RIN12(0) = 0, BIAS12 = 0<br>RIN12(0) = 0, BIAS12 = 1                                                                                                                   | -300<br>10                     |                                | -10<br>300                     | μA<br>μA                     |

| 103         | lin()        | Input Current                                        | RIN12(3:0) = 0x01                                                                                                                                                      | -10                            |                                | 10                             | μA                           |

| 104         | Rin()        | Input Resistance vs. VREFin                          | Tj = 27 °C;<br>RIN12(3:0) = 0x09<br>RIN12(3:0) = 0x00<br>RIN12(3:0) = 0x02<br>RIN12(3:0) = 0x04<br>RIN12(3:0) = 0x06                                                   | 16<br>1.1<br>1.6<br>2.2<br>3.2 | 20<br>1.6<br>2.3<br>3.2<br>4.6 | 24<br>2.1<br>3.0<br>4.2<br>6.0 | kΩ<br>kΩ<br>kΩ<br>kΩ<br>kΩ   |

| 105         | TCRin()      | Temperature Coefficient Rin                          |                                                                                                                                                                        |                                | 0.15                           |                                | %/K                          |

| 106         | VREFin12     | Reference Voltage                                    | RIN12(0) = 0, BIAS12 = 1<br>RIN12(0) = 0, BIAS12 = 0                                                                                                                   | 1.35<br>2.25                   | 1.5<br>2.5                     | 1.65<br>2.75                   | V                            |

| 107         | G12          | Selectable Gain Factors                              | RIN12(3:0) = 0x01, GR12 and GF12 = 0x0<br>RIN12(3:0) = 0x01, GR12 and GF12 = max.<br>RIN12(3:0) = 0x09, GR12 and GF12 = 0x0<br>RIN12(3:0) = 0x09, GR12 and GF12 = max. |                                | 2<br>100<br>0.5<br>25          |                                |                              |

| 108         | ∆Gdiff       | Differential Gain Accuracy                           | calibration range 11 bit                                                                                                                                               | -0.5                           |                                | 0.5                            | LSB                          |

| 109         | ⊿Gabs        | Absolute Gain Accuracy                               | calibration range 11 bit, guaranteed monotony                                                                                                                          | -1                             |                                | 1                              | LSB                          |

| 110         | Vin()diff    | Recommended Differential Input<br>Voltage            | Vin()diff = V(CHPx) - V(CHNx),<br>RUIN12(3) = 0<br>RUIN12(3) = 1                                                                                                       | 10<br>40                       |                                | 500<br>2000                    | mVpp<br>mVpp                 |

| 111         | Vin()os      | Input Offset Voltage                                 | refered to side of input                                                                                                                                               | 0                              | 20                             |                                | μV                           |

| 112         | VOScal       | Offset Calibration Range                             | referenced to the selected source (VOS12); ORx = 00 ORx = 01 ORx = 10 ORx = 11                                                                                         |                                | ±100<br>±200<br>±600<br>±1200  |                                | %V()<br>%V()<br>%V()<br>%V() |

| 113         | △VOSdiff     | Differential Linearity Error of Offset Correction    | calibration range 11 bit                                                                                                                                               | -0.5                           |                                | 0.5                            | LSB                          |

| 114         | ∆VOSint      | Integral Linearity Error of Offset Correction        | calibration range 11 bit                                                                                                                                               | -1                             |                                | 1                              | LSB                          |

| 115         | PHIkorr      | Phase Error Calibration Range                        | CH1 versus CH2                                                                                                                                                         |                                | ±10.4                          |                                | ٥                            |

| 116         | ∆PHIdiff     | Differential Linearity Error of<br>Phase Calibration | calibration range 10 bit                                                                                                                                               | -0.5                           |                                | 0.5                            | LSB                          |

| 117         | ∆PHlint      | Integral Linearity Error of Phase Calibration        | calibration range 10 bit                                                                                                                                               | -1                             |                                | 1                              | LSB                          |

| 119         | fin()max     | Permissible Input Frequency                          |                                                                                                                                                                        | 500                            |                                |                                | kHz                          |

| 120         | fhc()        | Input Amplifier Cut-off Frequency (-3dB)             |                                                                                                                                                                        | 250                            |                                |                                | kHz                          |

Rev D2, Page 7/29

### **ELECTRICAL CHARACTERISTICS**

| ltem<br>No. | Symbol       | Parameter                                         | Conditions                                                                                                      | Min.                           | Тур.                           | Max.                           | Unit                         |

|-------------|--------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|------------------------------|

| Signa       | I Condition  | ing, Inputs X1, X2                                |                                                                                                                 |                                |                                |                                |                              |

| 201         | Vin()sig     | Permissible Input Voltage Range                   | RIN0(3:0) = 0x01                                                                                                | 0.75                           |                                | VDDS<br>- 1.5                  | V                            |

|             |              |                                                   | RINO(3:0) = 0x09                                                                                                | 0                              |                                | VDDS                           | V                            |

| 202         | lin()sig     | Permissible Input Current Range                   | RIN0(0) = 0, BIAS0 = 0<br>RIN0(0) = 0, BIAS0 = 1                                                                | -300<br>10                     |                                | -10<br>300                     | μA<br>μA                     |

| 203         | lin()        | Input Current                                     | RIN0(3:0) = 0x01                                                                                                | -10                            |                                | 10                             | μA                           |

| 204         | Vout(X2)     | Output Voltage at X2                              | BIASEX = 10, I(X2) = 0, referenced to VREFin12                                                                  | 95                             | 100                            | 105                            | %                            |

| 205         | Vin(X2)      | Permissible Input Voltage at X2                   | BIASEX = 11                                                                                                     | 0.5                            |                                | VDDS<br>- 2                    | V                            |

| 206         | Rin(X2)      | Input Resistance at X2                            | BIASEX = 11, RIN0(3:0) = 0x01,<br>RIN12(3:0) = 0x01                                                             | 20                             | 27                             | 30                             | kΩ                           |

| 207         | Rin()        | Input Resistance vs. VREFin                       | Tj = 27 °C;<br>RIN0(3:0) = 0x09<br>RIN0(3:0) = 0x00<br>RIN0(3:0) = 0x02<br>RIN0(3:0) = 0x04<br>RIN0(3:0) = 0x06 | 16<br>1.1<br>1.6<br>2.2<br>3.2 | 20<br>1.6<br>2.3<br>3.2<br>4.6 | 24<br>2.1<br>3.0<br>4.2<br>6.0 | kΩ<br>kΩ<br>kΩ<br>kΩ         |

| 208         | TCRin()      | Temperature Coefficient Rin                       |                                                                                                                 |                                | 0.15                           |                                | %/K                          |

| 209         | VREFin0      | Reference Voltage                                 | RIN0(0) = 0, BIAS0 = 1<br>RIN0(0) = 0, BIAS0 = 0                                                                | 1.35<br>2.25                   | 1.5<br>2.5                     | 1.65<br>2.75                   | V                            |

| 210 G0      | G0           | Selectable Gain Factors                           | RIN0(3:0) = 0x01, GR0 and GF0 = 0x0<br>RIN0(3:0) = 0x01, GR0 and GF0 = max.                                     |                                | 2<br>100                       |                                |                              |

|             |              |                                                   | RIN0(3:0) = 0x09, GR0 and GF0 = 0x0<br>RIN0(3:0) = 0x09, GR0 and GF0 = max                                      |                                | 0.5<br>25                      |                                |                              |

| 211         | ∆Gdiff       | Differential Gain Accuracy                        | calibration range 5 bit                                                                                         | -0.5                           |                                | 0.5                            | LSE                          |

| 212         | ⊿Gabs        | Absolute Gain Accuracy                            | calibration range 5 bit, guaranteed monotony                                                                    | -1                             |                                | 1                              | LSB                          |

| 213         | Vin()diff    | Recommended Differential Input<br>Voltage         | Vin()diff = V(CHP0) - V(CHN0),<br>RIN0(3:0) = 0x01<br>RIN0(3:0) = 0x09                                          | 10<br>40                       |                                | 500<br>2000                    | mVp <sub>l</sub>             |

| 214         | Vin()os      | Input Offset Voltage                              | referred to side of input                                                                                       | 0                              | 75                             |                                | μV                           |

| 215         | VOScal       | Offset Calibration Range                          | referenced to the selected source (REFVOS);<br>OR0 = 00<br>OR0 = 01<br>OR0 = 10<br>OR0 = 11                     |                                | ±100<br>±200<br>±600<br>±1200  |                                | %V()<br>%V()<br>%V()<br>%V() |

| 216         | ∆VOSdiff     | Differential Linearity Error of Offset Correction | calibration range 6 bit                                                                                         | -0.5                           |                                | 0.5                            | LSB                          |

| 217         | △VOSint      | Integral Linearity Error of Offset Correction     | calibration range 6 bit                                                                                         | -1                             |                                | 1                              | LSB                          |

| Signa       | l Filter     |                                                   |                                                                                                                 |                                |                                |                                |                              |

| 301         | fg           | Cut-off Frequency                                 |                                                                                                                 |                                |                                | 4000                           | kHz                          |

| 302         | phi          | Phase Shift                                       | fin 500 kHz for sine/cosine                                                                                     |                                |                                | 10                             | ۰                            |

| Index       | Pulse Com    | parator Output PZ, NZ                             |                                                                                                                 |                                |                                |                                |                              |

| 401         | Vpk()        | Output Amplitude With Sensor<br>Tracking via ACO  | EAZ = 1, ADJ(4:0) = 0x19                                                                                        | 225                            | 250                            | 275                            | mV                           |

| 402         | SR()         | Output Slew Rate                                  | EAZ = 1                                                                                                         |                                | 1                              |                                | V/µs                         |

| Line [      | Priver Outpo | uts PS, NS, PC, NC, PZ, NZ                        |                                                                                                                 |                                |                                |                                |                              |

| 501         | Vpk()max     | Permissible Output Amplitude                      | VDD = 4.5 V, DC level = VDD / 2,<br>RL = $50 \Omega$ vs. VDD / 2                                                |                                |                                | 300                            | mV                           |

| 502         | Vpk()        | Output Amplitude With Sensor<br>Tracking via ACO  | ADJ (8:0) = 0x19                                                                                                | 225                            | 250                            | 275                            | mV                           |

| 503         | fg           | Cut-off Frequency                                 | CL = 250 pF                                                                                                     | 500                            |                                |                                | kHz                          |

| 504         | Vos          | Offset Voltage                                    |                                                                                                                 |                                | ±200                           |                                | μV                           |

| 505         | lsc()        | Short-circuit Current                             | pin shorten to VDD or GND                                                                                       | 10                             | 30                             | 50                             | mA                           |

| 506         | Ilk()        | Tristate Leakage Current                          | tristate or reversed supply                                                                                     | -1                             |                                | 1                              | μA                           |

|             |              |                                                   | 117                                                                                                             |                                |                                |                                |                              |

Rev D2, Page 8/29

### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VDD = 4.3...5.5 V, Tj = -40...125 °C, IBN calibrated to 200 μA, reference point GNDS, unless otherwise stated.

| Item<br>No. | Symbol       | Parameter                                      | Conditions                                                                                                                                               | Min.                      | Тур. | Max.                    | Unit                 |

|-------------|--------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|-------------------------|----------------------|

|             | Level Con    | troller ACO                                    |                                                                                                                                                          | Ш                         |      | ı                       | ш                    |

| 601         | Vs()hi       | Saturation Voltage hi at ACO vs. VDD           | Vs() = VDD - V();<br>ADJ(8:0) = 0x11F, I() = -5 mA<br>ADJ(8:0) = 0x13F, I() = -10 mA<br>ADJ(8:0) = 0x15F, I() = -25 mA<br>ADJ(8:0) = 0x17F, I() = -50 mA |                           |      | 1<br>1<br>1<br>1        | V<br>V<br>V          |

| 602         | Isc()hi      | Short-circuit Current hi in ACO                | V() = 0 VDD - 1 V;<br>ADJ(8:0) = 0x11F<br>ADJ(8:0) = 0x13F<br>ADJ(8:0) = 0x15F<br>ADJ(8:0) = 0x17F                                                       | -10<br>-20<br>-50<br>-100 |      | -5<br>-10<br>-25<br>-50 | mA<br>mA<br>mA<br>mA |

| 603         | tr()         | Current Rise Time in ACO                       | I(ACO): 0 → 90 % setpoint                                                                                                                                |                           | 1    |                         | ms                   |

| 604         | tset()       | Current Settling Time in ACO                   | Square control active, I(ACO): $50 \rightarrow 100 \%$ setpoint                                                                                          |                           | 400  |                         | μs                   |

| 605         | It()min      | Control Range Monitoring 1: lower limit        | referenced to range ADJ(6:5)                                                                                                                             |                           | 3    |                         | %lsc                 |

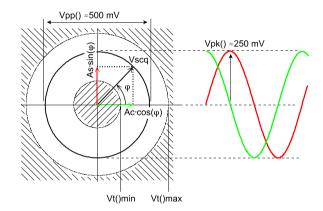

| 606         | It()max      | Control Range Monitoring 2: upper limit        | referenced to range ADJ(6:5)                                                                                                                             |                           | 90   |                         | %lsc                 |

| 607         | Vt()min      | Signal Level Monitoring 1: lower limit         | referenced to Vscq()                                                                                                                                     |                           | 40   |                         | %Vpr                 |

| 608         | Vt()max      | Signal Level Monitoring 2: upper limit         | referenced to Vscq()                                                                                                                                     |                           | 130  |                         | %Vpp                 |

|             | urrent ERF   | ?                                              |                                                                                                                                                          |                           |      |                         | 11                   |

|             | I(ERR)       | Permissible Test Current                       | test mode activated                                                                                                                                      | 0                         |      | 1                       | mA                   |

|             | 1            | rce and Reference Voltages                     |                                                                                                                                                          |                           |      |                         | 11                   |

| 801         | IBN()        | Bias Current Source                            | MODE(3:0) = 0x01, I(NC) vs. VDDS                                                                                                                         | 180                       | 200  | 220                     | μA                   |

| 802         | VPAH         | Reference Voltage VPAH                         | referenced to GND                                                                                                                                        | 45                        | 50   | 55                      | %VDI                 |

| 803         | V05          | Reference Voltage V05                          |                                                                                                                                                          | 450                       | 500  | 550                     | mV                   |

| 804         | V025         | Reference Voltage V025                         |                                                                                                                                                          |                           | 50   |                         | %V05                 |

|             | -Down-Res    |                                                | in an a sign welfare at V/DD we CND                                                                                                                      | 0.7                       |      | 4.0                     |                      |

| 901         | VDDon        | Turn-on Threshold<br>(power-on release)        | increasing voltage at VDD vs. GND                                                                                                                        | 3.7                       | 4    | 4.3                     | V                    |

| 902         | VDDoff       | Turn-off Threshold<br>(power-down reset)       | decreasing voltage at VDD vs. GND                                                                                                                        | 3.2                       | 3.5  | 3.8                     | V                    |

| 903         | VDDhys       | Threshold Hysteresis                           | VDDhys = VDDon - VDDoff                                                                                                                                  | 0.3                       |      |                         | V                    |

|             | Oscillator   | T                                              |                                                                                                                                                          |                           |      | T                       | ı                    |

| _           | fclk()       | Internal Clock Frequency                       | MODE(3:0) = 0x0A, fclk(NS)                                                                                                                               | 120                       | 160  | 200                     | kHz                  |

|             | <del>,</del> | ot/Output, Pin ERR                             | CND I/) A A                                                                                                                                              |                           |      | 0.4                     |                      |

| B01<br>B02  | Vs()lo       | Saturation Voltage lo Short-circuit Current lo | vs. GND, I() = 4 mA<br>vs. GND; V(ERR) ≤ VDD                                                                                                             | Α                         |      | 0.4                     | V<br>m^              |

| DU2         | ISC()        | Short-circuit Current to                       | V(ERR) > VTMon                                                                                                                                           | 4 2                       |      |                         | mA<br>mA             |

| B03         | Vt()hi       | Input Threshold Voltage hi                     | vs. GND                                                                                                                                                  |                           |      | 2                       | V                    |

| B04         | Vt()lo       | Input Threshold Voltage lo                     | vs. GND                                                                                                                                                  | 0.8                       |      |                         | V                    |

| B05         | Vt()hys      | Input Hysteresis                               | Vt()hys = Vt()hi - Vt()lo                                                                                                                                | 300                       | 500  |                         | mV                   |

| B06         | lpu()        | Input Pull-up Current                          | V() = 0VDD - 1 V, EPU = 1                                                                                                                                | -400                      | -300 | -200                    | μA                   |

| B07         | Rpu()        | Input Pull-Up Resistor                         | EPU=0                                                                                                                                                    |                           | 500  |                         | kΩ                   |

| B08         | Vpu()        | Pull-up Voltage                                | $Vpu() = VDD - V(), I() = -5 \mu A, EPU = 1$                                                                                                             |                           |      | 0.4                     | V                    |

| B09         | VTMon        | Test Mode Activation Threshold                 | increasing voltage at ERR                                                                                                                                |                           |      | VDD +<br>1.5            | V                    |

| B10         | VTMoff       | Test Mode Disabling Threshold                  | decreasing voltage at ERR                                                                                                                                | VDD +<br>0.5              |      |                         | V                    |

| B11         | VTMhys       | Test Mode Hysteresis                           | VTMhys = VTMon — VTMoff                                                                                                                                  | 0.15                      | 0.3  |                         | V                    |

| B12         | llk()        | Leakage Current                                | tristate or reversed supply voltage                                                                                                                      | -1                        | -10  | -50                     | μA                   |

Rev D2, Page 9/29

### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VDD = 4.3...5.5 V, Tj = -40...125 °C, IBN calibrated to 200 µA, reference point GNDS, unless otherwise stated.

| ltem<br>No. | Symbol           | Parameter                                                    | Conditions                                                                                                   | Min.       | Тур.                    | Max.             | Unit           |

|-------------|------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------|-------------------------|------------------|----------------|

| IqquS       | ∪<br>v Switch an | d Reverse Polarity Protection VD                             | DDS. GNDS                                                                                                    | 1          | 7.                      |                  |                |

| - • •       | Vs()             | Saturation Voltage<br>VDDS vs. VDD                           | Vs(VDDS) = VDD - V(VDDS)<br>I(VDDS) = -10 mA0 mA<br>I(VDDS) = -20 mA10 mA                                    |            |                         | 150<br>250       | mV<br>mV       |

| C02         | Vs()             | Saturation Voltage<br>GNDS vs. GND                           | Vs(GNDS) = V(GNDS) - GND<br>I(GNDS) = 0 mA10 mA<br>I(GNDS) = 10 mA20 mA                                      |            |                         | 150<br>250       | mV<br>mV       |

| Serial      | Configurat       | ion Interface SCL, SDA                                       |                                                                                                              |            |                         |                  |                |

| D01         | Vs()lo           | Saturation Voltage lo                                        | I() = 4 mA                                                                                                   |            |                         | 400              | mV             |

| D02         | Isc()            | Short-circuit Current lo                                     |                                                                                                              | 4          |                         | 80               | mA             |

| D03         | Vt()hi           | Input Threshold Voltage hi                                   |                                                                                                              |            |                         | 2                | V              |

| D04         | Vt()lo           | Input Threshold Voltage lo                                   |                                                                                                              | 0.8        |                         |                  | V              |

| D05         | Vt()hys          | Input Hysteresis                                             | Vt()hys = $Vt()$ hi – $Vt()$ lo                                                                              | 300        | 500                     |                  | mV             |

| D06         | lpu()            | Input Pull-up Current                                        | V() = 0VDDS - 1 V                                                                                            | -600       | -300                    | -60              | μA             |

| D07         | Vpu()            | Input Pull-up Voltage                                        | Vpu() = VDDS - V(), I() = -5 μA                                                                              |            |                         | 0.4              | V              |

| D08         | fclk(SCL)        | Clock Frequency at SCL                                       | ENFAST = 0<br>ENFAST = 1                                                                                     | 60<br>240  | 80<br>320               | 100<br>400       | kHz<br>kHz     |

| D09         | tbusy()cfg       | Duration of Startup Configuration                            | IBN not calibated, EEPROM access without read failure, time to outputs operational; ENFAST = 0 ENFAST = 1    |            | 40<br>25                | 55<br>35         | ms<br>ms       |

| D10         | tbusy()err       | End Of I2C Communication;<br>Time Until I2C Slave Is Enabled | IBN not calibrated;<br>V(SDA) = 0 V<br>V(SCL) = 0 V or arbitration lost<br>no EEPROM<br>CRC ERROR            |            | 4<br>indef.<br>45<br>95 | 12<br>135<br>285 | ms<br>ms<br>ms |

| D11         | td()             | Start Of Master Activity On I2C<br>Protocol Error            | SCL without clock signal: V(SCL) = constant;<br>IBN not calibrated<br>IBN calibrated to 200 µA               | 25<br>64   | 80<br>80                | 240<br>120       | μs<br>μs       |

| D12         | td()i2c          | Delay for I2C-Slave-Mode Enable                              | no EEPROM, V(SDA) = 0 V                                                                                      |            | 4                       | 6.2              | ms             |

| Temp        | erature Mon      | nitoring                                                     | , ,                                                                                                          |            |                         |                  |                |

| E01         | VTs              | Temperature Sensor Voltage                                   | VTs() = VDDS - V(PS), Tj = 27 °C,<br>Calibration Mode 3, no load                                             | 600        | 650                     | 700              | mV             |

| E02         | TCs              | Temp. Co. of Temperature Sensor Voltage                      |                                                                                                              |            | -1.8                    |                  | mV/K           |

| E03         | VTth             | Temperature Warning Activation<br>Threshold                  | VTth() = VDDS - V(NS), Tj = 27 °C,<br>Calibration Mode 3, no load;<br>CFGTA(3:0) = 0x00<br>CFGTA(3:0) = 0x0F | 260<br>470 | 310<br>550              | 360<br>630       | mV<br>mV       |

| E04         | TCth             | Temp. Co. Temperature Warning Activation Threshold           |                                                                                                              |            | 0.06                    |                  | %/K            |

| E05         | Thys             | Temperature Warning Hysteresis                               |                                                                                                              | 4          | 12                      | 20               | °C             |

| E06         | ΔΤ               | Relative Shutdown Temperature                                | $\Delta T = Toff - Twarn$                                                                                    | 4          | 12                      | 20               | °C             |

Input-to-output Feedthrough

BYP

# iC-MSB<sup>SAFETY</sup>, iC-MSB2 SIN/COS SIGNAL CONDITIONER WITH 1Vpp DRIVER

Rev D2, Page 10/29

### **PROGRAMMING**

| Register Map                                                                                                        | Page 11                                                                                                                                                                                                                                                                                                                                                                                                 | Signal Condi                                                            | tioning CH1, CH2 (X3X6) Page 21                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                         | GR12:                                                                   | Gain Range CH1, CH2 (coarse)                                                                                                                                                                                                                                                                               |

|                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                         | GF1:                                                                    | Gain Factor CH1 (fine)                                                                                                                                                                                                                                                                                     |

|                                                                                                                     | n Interface Page 13                                                                                                                                                                                                                                                                                                                                                                                     | GF2:                                                                    | Gain Factor CH2 (fine)                                                                                                                                                                                                                                                                                     |

| ENFAST:                                                                                                             | I <sup>2</sup> C Fast Mode Enable                                                                                                                                                                                                                                                                                                                                                                       | VOS12:                                                                  | Offset Reference Source CH1, CH2                                                                                                                                                                                                                                                                           |

| ENSL:                                                                                                               | I <sup>2</sup> C Slave Mode Enable                                                                                                                                                                                                                                                                                                                                                                      | VDC1:                                                                   | Intermediate Voltage CH1                                                                                                                                                                                                                                                                                   |

| DEVID:                                                                                                              | Device ID of EEPROM providing the                                                                                                                                                                                                                                                                                                                                                                       | VDC2:                                                                   | Intermediate Voltage CH2                                                                                                                                                                                                                                                                                   |

|                                                                                                                     | chip configuration data (e.g. 0x50)                                                                                                                                                                                                                                                                                                                                                                     | OR1:                                                                    | Offset Range CH1 (coarse)                                                                                                                                                                                                                                                                                  |

| CHKSUM:                                                                                                             | CRC of chip configuration data                                                                                                                                                                                                                                                                                                                                                                          | OF1:                                                                    | Offset Factor CH1 (fine)                                                                                                                                                                                                                                                                                   |

|                                                                                                                     | (address range 0x00 to 0x1E)                                                                                                                                                                                                                                                                                                                                                                            | OR2:                                                                    | Offset Range CH2 (coarse)                                                                                                                                                                                                                                                                                  |

| CHPREL:                                                                                                             | Chip Release                                                                                                                                                                                                                                                                                                                                                                                            | OF2:                                                                    | Offset Factor CH2 (fine)                                                                                                                                                                                                                                                                                   |

| NTRI:                                                                                                               | Tristate Function and                                                                                                                                                                                                                                                                                                                                                                                   | PH12:                                                                   | Phase Correction CH1 vs. CH2                                                                                                                                                                                                                                                                               |

|                                                                                                                     | Op. Mode Change                                                                                                                                                                                                                                                                                                                                                                                         |                                                                         |                                                                                                                                                                                                                                                                                                            |

|                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                         | tioning CH0 (X1, X2) Page 23                                                                                                                                                                                                                                                                               |

|                                                                                                                     | Page 15                                                                                                                                                                                                                                                                                                                                                                                                 | GR0:                                                                    | Gain Range CH0 (coarse)                                                                                                                                                                                                                                                                                    |

| CFGIBN:                                                                                                             | Bias Calibration                                                                                                                                                                                                                                                                                                                                                                                        | GF0:                                                                    | Gain Factor CH0 (fine)                                                                                                                                                                                                                                                                                     |

| CFGTA:                                                                                                              | Temperature Sensor Calibration                                                                                                                                                                                                                                                                                                                                                                          | VOS0:                                                                   | Offset Reference Source CH0                                                                                                                                                                                                                                                                                |

|                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                         | OR0:                                                                    | Offset Range CH0 (coarse)                                                                                                                                                                                                                                                                                  |

|                                                                                                                     | odes Page 16                                                                                                                                                                                                                                                                                                                                                                                            | OF0:                                                                    | Offset Factor CH0 (fine)                                                                                                                                                                                                                                                                                   |

| MODE:                                                                                                               | Operation Mode                                                                                                                                                                                                                                                                                                                                                                                          |                                                                         |                                                                                                                                                                                                                                                                                                            |

|                                                                                                                     | •                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                         |                                                                                                                                                                                                                                                                                                            |

| ENF:                                                                                                                | Signal Filtering                                                                                                                                                                                                                                                                                                                                                                                        |                                                                         | Controller Page 24                                                                                                                                                                                                                                                                                         |

|                                                                                                                     | -                                                                                                                                                                                                                                                                                                                                                                                                       | <b>Signal Level</b><br>ADJ:                                             | Controller Page 24 Setup of ACO Output Function                                                                                                                                                                                                                                                            |

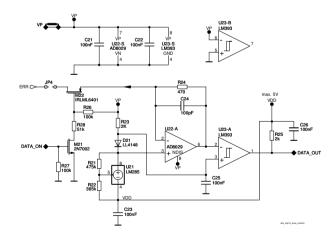

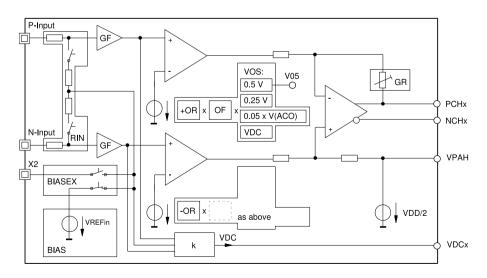

| Test Mode                                                                                                           | Seite 17                                                                                                                                                                                                                                                                                                                                                                                                | ADJ:                                                                    | Setup of ACO Output Function                                                                                                                                                                                                                                                                               |